Verifying Additive Phase Noise And Jitter Attenuation Of PLLs In High-Speed Digital Designs

Source: Rohde & Schwarz GmbH & Co. KG

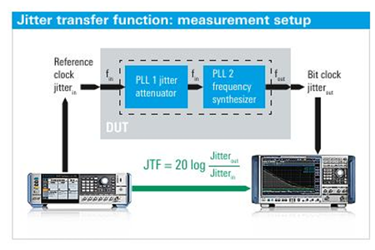

Increasing data rates in high-speed digital designs and wireless communications require SerDes PLLs and clock synthesizers with low additive phase noise and high jitter attenuation. Modern designs often follow a two-stage architecture comprising a jitter-attenuator and a frequency-synthesizer stage. Phase noise analyzers are the choice instruments for these tests due to their high phase noise sensitivity. This application note presents a phase noise analyzer solution to test the additive phase noise and jitter transfer function of PLLs. Download the full paper for more information.

access the Application Note!

Log In

Get unlimited access to:

Trend and Thought Leadership Articles

Case Studies & White Papers

Extensive Product Database

Members-Only Premium Content

Welcome Back! Please Log In to Continue.

X

Enter your credentials below to log in. Not yet a member of Wireless Design Online? Subscribe today.

Subscribe to Wireless Design Online

X

Subscribe to Wireless Design Online

This website uses cookies to ensure you get the best experience on our website. Learn more